Introduction to eFPGAs

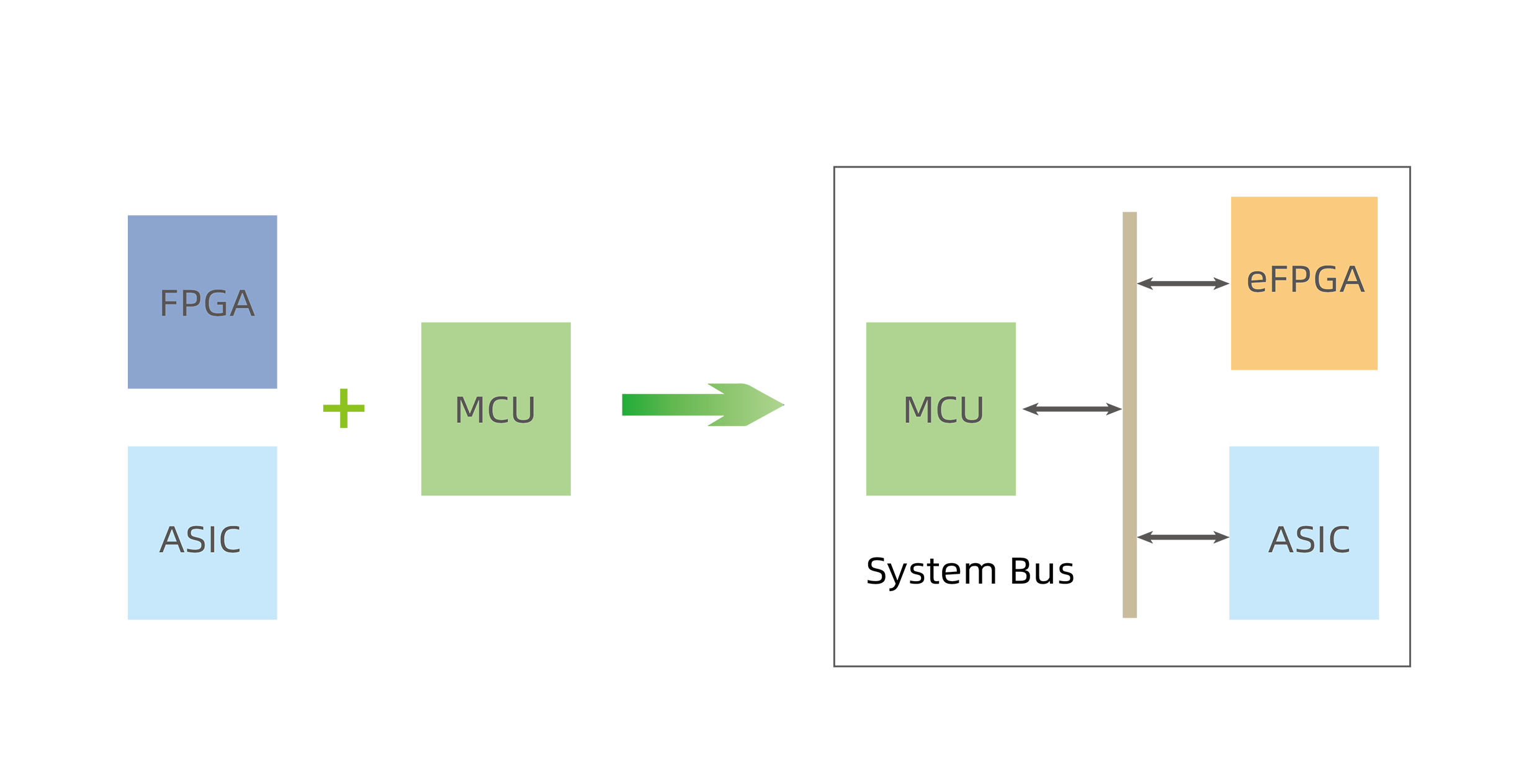

eFPGA (Embedded FPGA), that is, embedded FPGA, which integrates FPGA as IP into SOC/ASIC chips, while maintaining the flexibility of FPGAs, its cost and power consumption are much lower than FPGA chips.

eFPGAs bring "flexibility" to chip products: by adding eFPGAs, SoC/ASIC products can be reconfigured for design; SoC/ASIC products can be adapted to different markets, increasing market capacity and extending the product life of SoC/ASIC. In addition, the use of eFPGAs can reduce the R&D cycle and development cost of new products. With the increase in the technical complexity and R&D cost of chips, as well as the increasingly fierce competition in the market, eFPGA will be more and more accepted by the market and become an important solution in the field of chip design.

FIG. 1 Schematic diagram of eFPGA products

eFPGA products have the following advantages:

eFPGA products have the following advantages:

![]() Compared to ASIC, eFPGA is reconfigurable and more flexible:

Compared to ASIC, eFPGA is reconfigurable and more flexible:

![]() Compared with FPGA, eFPGA is more secure and not easy to be cracked and copied.

Compared with FPGA, eFPGA is more secure and not easy to be cracked and copied.

![]() Compared to FPGAs, eFPGAs have higher performance and lower power consumption

Compared to FPGAs, eFPGAs have higher performance and lower power consumption

![]() Compared to FPGAs, eFPGAs are less expensive

Compared to FPGAs, eFPGAs are less expensive

Custom eFPGA products

Custom eFPGA products

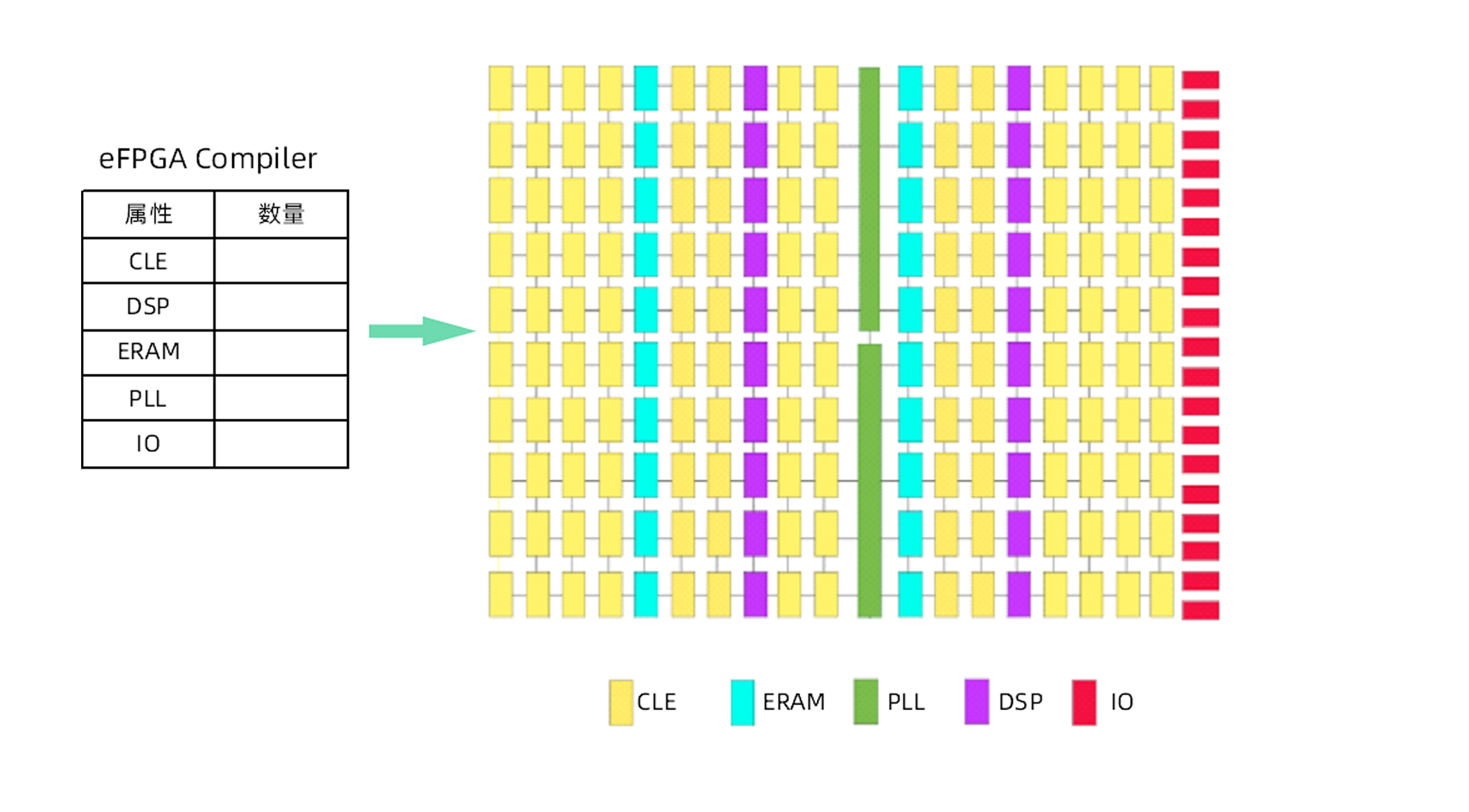

As shown in the figure, users can customize the eFPGA IP according to their own needs through the eFPGA Compiler tool provided by Zhongke Xinmagnetic Technology. Users can customize the eFPGA according to the number of CLE, Register, DSP, ERAM, and PLL in the eFPGA Compiler.

Figure eFPGA Compiler Generates eFPGA

eFPGA development tool introduction

eFPGA development tool introduction

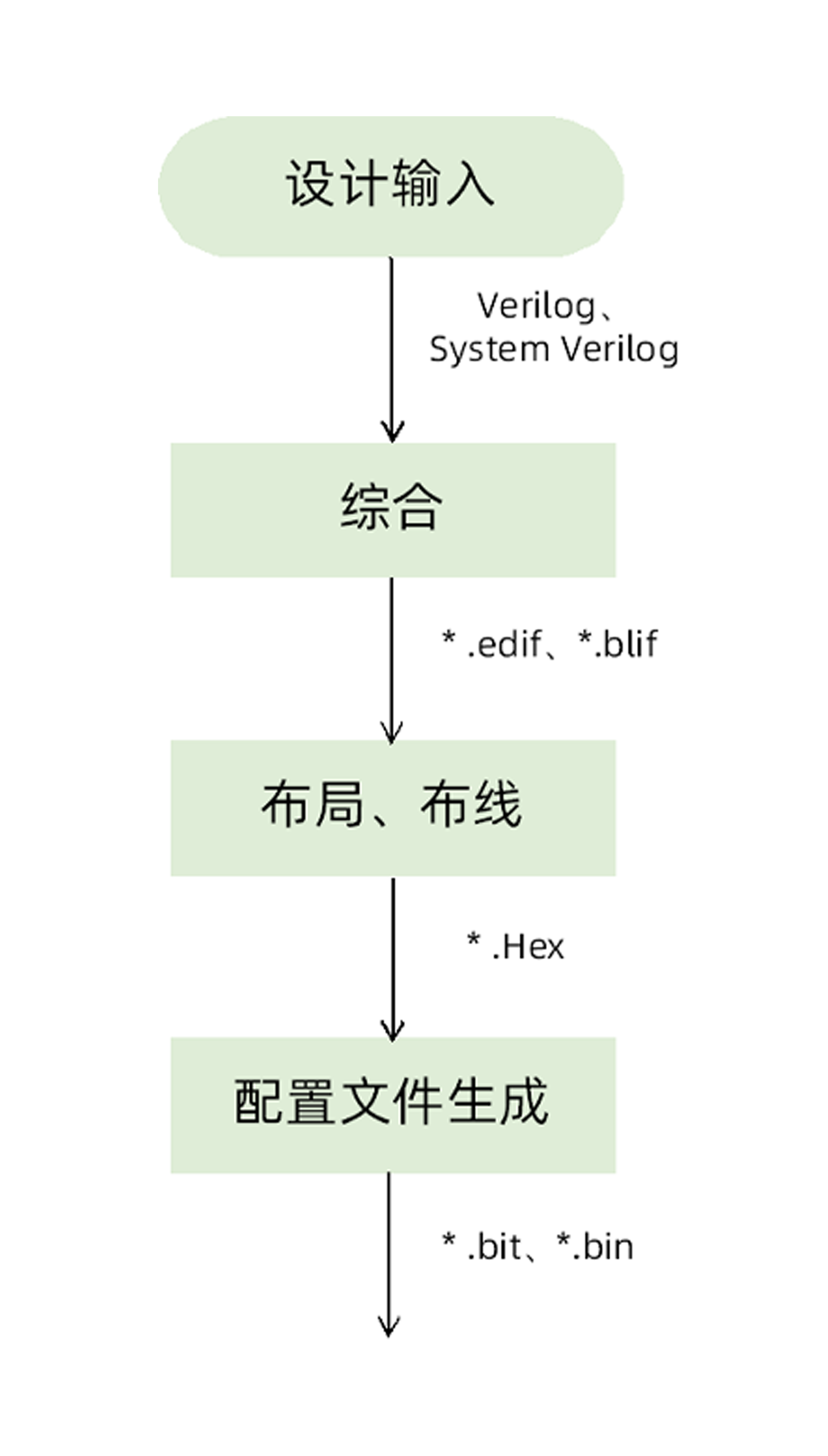

Chipmagnetics provides a full-process development tool for eFPGA to realize the synthesis, layout, wiring and Bitstream generation functions of user design. To speed up the design process, the eFPGA development tool supports the following IPs:

|

|

Figure eFPGA development process |